80核架构与硅光芯片即将到来

6月18日,2009年Intel研究日在美国加州山景市拉开了帷幕,向世界展示了未来技术的发展趋势。本次Intel研究日通过环保技术、3D互联网、企业IT和无线移动等四大技术展区展示了近40项前瞻性研究项目和概念,其中在万亿次计算与光传输的革命性突破尤其为外界所瞩目。为此,本刊特派记者采集到大量一手信息,并对Intel新的80核架构和硅光芯片技术进行深入分析报道。

6月18日,2009年Intel研究日在美国加州山景市拉开了帷幕,向世界展示了未来技术的发展趋势。本次Intel研究日通过环保技术、3D互联网、企业IT和无线移动等四大技术展区展示了近40项前瞻性研究项目和概念,其中在万亿次计算与光传输的革命性突破尤其为外界所瞩目。为此,本刊特派记者采集到大量一手信息,并对Intel新的80核架构和硅光芯片技术进行深入分析报道。

作为计算市场的三驾马车,Intel、NVIDIA与AMD都有雄心勃勃的未来计划。NVIDIA一再否认外界对于其将进入x86市场的推测,而强调GPU将取代CPU、成为计算系统中重要的处理芯片,同时NVIDIA不断与软件业界合作、推动CUDA通用平台成为事实的标准。AMD则祭出Fusion混合计算概念,将CPU和图形技术完美地进行整合,实现一体化计算。而作为行业的领袖,Intel在处理器市场维持惯有强势的同时,还宣布了Larrabee高并行处理器,试图打造一套基于x86的通用计算和高端图形平台─但这仅是Intel新一轮技术革命的开始:光传输与万亿次计算计划才是Intel未来的远期目标。

Intel“万亿级计算”与GPU通用计算大不相同

利用效率更高的处理器来完成高并行浮点计算是计算工业的共识。这类计算遍布3D游戏渲染、电影特效制作、高清视频处理、虚拟现实、生物计算(比如DNA配序)、气象模拟、太空探索等,它们所处理的数据是单精度浮点或双精度浮点,具有高并行度、彼此相互独立的特点。

上个世纪90年代,3dfx的Voodoo显卡为PC打开了3D渲染大门,NVIDIA则开拓了独立的GPU时代。之后,3D渲染便由效率更高的GPU来完成,而其它高并行计算一般属于专业领域,不可能发展出一一对应的专用芯片,所以这类任务通常都交给超级计算机处理,但这些特殊的计算机里往往装载了数千颗强大的处理器。

伴随着时间的推移,GPU拥有越来越强大的浮点性能,统一渲染架构又赋予了GPU更强的灵活性。在NVIDIA的推动下,GPU进入通用计算领域,尤其是在这些高并行处理应用中表现出卓越的性能。但GPU本身架构不够灵活,如果要让GPU能够执行这些计算任务,用户必须重新编制它们的软件,不仅难度大,而且用途较为狭窄。

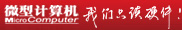

图1 万亿次计算将为PC用户带来超乎想象的体验

早在2007年,Intel就提出万亿级计算将进入桌面的构想,并同时设立了一个雄心勃勃的“万亿级计算(Tera-scale computing)”远期项目。与GPU通用加速不同,万亿次计算同时针对桌面和专业应用,它将为PC用户带来超乎想象的体验:

●你在观看体育节目的同时,计算机视觉软件可以将体育节目中数十万个视频帧挖掘出来,并总结成一小段视频─若利用现有的计算平台,那么需要花费数小时方可完成,而万亿级计算平台几乎可以实时完成这些任务。

●实现用户与虚拟环境的高度整合,比如未来的游戏可以利用多个摄像头识别你与你的动作,接着提取出骨骼模型,利用光线追踪技术创建出高度逼真的虚拟模型,让你成为虚拟游戏里面的“真实角色”─这项任务现在只能离线处理,但是通过万亿级处理器,我们就能够实时完成。

●在很短的时间内,也许只是十多分钟,将几十年来值得珍藏的照片和家庭录像编辑成一段几分钟的节目,然后在家庭成员的生日聚会上播放。

●创建基于网络的虚拟办公室和虚拟企业,企业可以没有任何实体办公点,但在网络空间中,大家能以真实面貌高效协作。

当然,万亿级计算还将有更多的可能性:面向智能汽车和设备的人工智能(AI);针对建模、虚拟化、物理模拟和医疗培训的虚拟现实(VR);以及其它仍属于科幻小说范畴的超前应用;可以预见,万亿级计算将拥有无限可能。

万亿级计算的架构实现

由于GPU首先必须考虑到图形渲染,这就注定了它无法获得高度灵活性,GPU通用计算更多只是单个应用上的有限延伸。Intel“万亿级计算”以不同的契合点进入,即优先于上述通用计算,架构灵活性成为重要的因素。该项目的科学家认为,超级多核架构是实现上述万亿级计算的唯一可行方向,因此整个项目都围绕超级多核计算架构的构建来进行(图2)。

图2 超级多核架构是实现万亿级计算的唯一可行方向,而其平台看上去也与普通平台大相径庭

现在的GPU虽然拥有超过1Teraflops的计算能力,但它所指的是单精度浮点,双精度浮点性能一般只有其十分之一。但是,超多核处理器的计算核心之间必须频繁交换大量的数据,核心通信都通过芯片上的互连(interconnection)网络负责,事实上这也是超多核处理器设计中难度大的部分。

如果处理器只有两个核心,那么核心间通信可以通过共享缓存,如果核心数量更多一些,那么可以为它们开辟直连通道,但如果要满足超过80个核心的高效通信,设计者们必须非常谨慎。简而言之,片上互连网络的设计必须考虑三个因素,即功耗、芯片面积以及设计复杂度。

1.功耗

片上互连网络是个耗电大户,耗电量高达芯片整体耗电量的三分之一。如增加片上互连网络带宽,就会增加能耗。所以设计者一方面要考虑实际带宽的需求,也必须考虑到电源管理技术方面的限制,达到按需供应,以节约电能。

2.芯片面积

片上互连网络也是由芯片中的一部分晶体管构成的,在芯片上占用的面积可超过内核晶核面积的五分之一。倘若用了太多的晶体管作互连网络,用于计算功能的晶体管数量就会减少。因此设计者们必须找到一个合理的比例,不能牺牲太多计算功能区域,也就是说互连网络的片上面积是有限制的。

3.设计复杂度

在各种类型的网络结构中,总线(BUS)简单,但一次只能收或是发一个消息;双向的环结构(Ring)可以做到同时收发,链路速度也快,但是内核大量增加后效率不高。增加到二维的网状网络(mesh)是理想选择:它可以处理大量并发消息,又有大量的路由可供选择。如果继续增加维度,在交叉开关矩阵(Crossbar)的控制下,任意核心都可以同其它任意核心建立通信,这样的高维网络显然拥有更好的性能,但设计难度也大。

在详细分析的基础上,Intel的研究者认为,在万亿级系统中,芯片整体带宽要达到TB/s(每秒万亿字节)的水平,链路带宽要在数百GB/s级别。研究人员在基于性能、芯片面积和能耗等相关因素后,确定将采用二维网状网络作为万亿级芯片的片上互连方案。这个方案兼顾能源消耗、晶体管开销和传输性能,但它仍然只是权宜之计。Intel雄心勃勃计划用光传输来代替电子传输,以彻底解决超多核处理器间的核心通信问题─光传输可以轻松做到TB/s的总带宽和数百GB/s的核心直连,同时功耗、发热极低,晶体管占用很小,是超多核处理器的佳选择。我们必须注意,光传输并不是纯粹的构想,Intel在多年前就认为现有的电路技术将会遭遇瓶颈,光传输将取而代之。为此,Intel与加州大学圣芭芭拉分校联手进行硅光技术的基础研究,双方致力于将光传输与半导体硅技术结合起来,并获得斐然成果。Intel希望在未来的万亿级处理器中,全面采用硅光传输来代替现有的电路传输。

Intel展示的80核处理器原型:Teraflop Research Chip

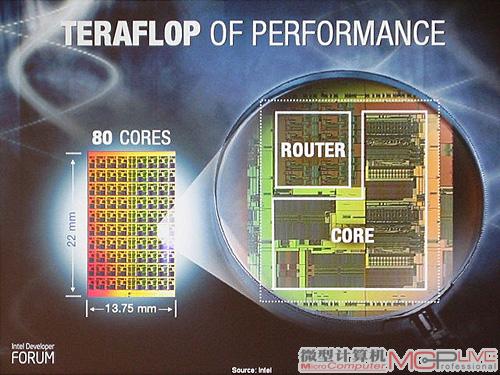

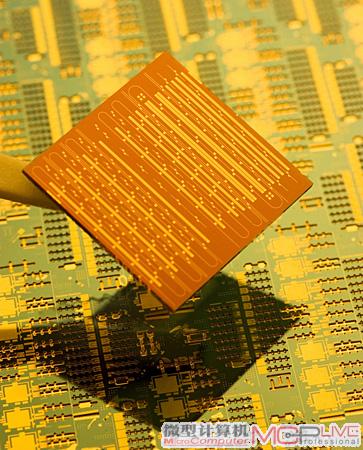

2008年10月,Intel公开展出首款80核处理器原型:Teraflop Research Chip,它也是Intel公司在“万亿级计算”研究领域内取得的新成果。在这次的研究日上,Intel的研究人员向我们进一步披露了这款芯片的详细信息(图3)。

图3 Teraflop Research Chip:Intel的万亿级研究芯片原型

从外观上看,Teraflop Research Chip封装和一般的x86处理器要大一些(图4),但核心尺寸也只有275mm2,和指甲盖差不多大小;这款芯片内配置了80个处理器内核,默认频率下耗电量只有

62W,功耗甚至比目前许多桌面处理器低。当然,这个原型芯片内集成的仅是简单的浮点计算单元,因此芯片规模可以很小,仅作为研究和展示用途。

图4 Teraflop Research Chip处理器实物

Teraflop Research Chip的默认运行频率为3.16GHz,此时它可提供1.01Teraflops的浮点计算性能,芯片内部互连总带宽为1.62Terabits/s(也就是0.2TB/s)。如果将电压增加到1.2V,那么

Teraflop Research Chip的工作频率可以提高到5.1GHz,此时计算能力达到1.63Teraflop,不过功耗也猛增至175W。如加压至1.25V,芯片频率将进一步提升到5.7GHz,此时其计算性能为

1.81Teraflop,功耗则达到265W─虽然其计算性能非常强悍,但我们也可以看到随着频率增加,耗电量的增幅大于性能的增幅,估计高功耗也将成为Intel未来超多核计划的又一重大挑战。

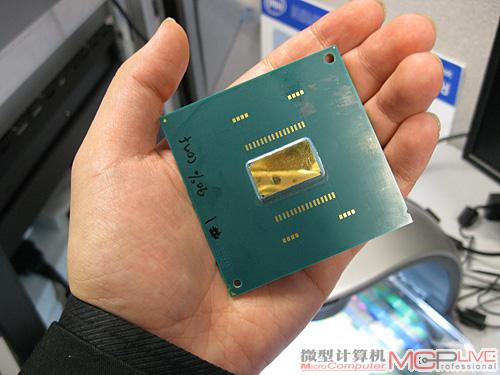

图5 Teraflop Research Chip芯片的晶圆

在芯片布局方面,Teraflop Research Chip也非常特殊,它被设计成8×10结构的晶体管阵列,每个基本单元称为一个“块面(Tile)”,块面包括一个微小的内核(或者是计算单元)和一个路由器。其中,内核含有一些能够生成数据的简单指令,而路由器则负责与高速缓存和相邻块面的连接。

图6 Teraflop Research Chip演示平台,在巨大散热器下的就是

这个80核的原型处理器,整个平台通过特殊的IO与外界连接。系统

通过一台现有的普通PC来控制这个平台进行设定好的一些运算脚本

Teraflop Research Chip的每个内核都拥有256KB高速缓存,不过它并不是像常规处理器一样,以平面方式与CPU核心电路直接集成,而是基于硅核植入(Through silicon Vias)技术的3维堆叠式内存。这项技术的基本原理是将缓存芯片和CPU芯片叠放在一起,电源和I/O信号从内存穿过到达CPU;每个内核都与3维堆叠内存直接相连。Teraflop Research Chip的每个CPU内核都配备256KB SRAM高速缓存(累计有20MB),CPU与SRAM间共有8490个连接点─由于每个内核都与3维堆叠缓存相连,系统同时满足了大容量和低延迟传输的要求。研究人员表示,该技术目前已在小批量生产中实现,下一步的研究计划是如何将这套方案推广到大规模量产的生产工艺,但我们相信该技术出现在商用产品中也只是一个时间问题(图5)。

图7 Teraflop Research Chip平台的演示:将不断晃动的视频

(摄影师骑在马上,左图)实时处理为稳定的视频画面(右图)

从数字上看,Teraflop Research Chip的计算能力堪比现在的顶级GPU,但实际上Teraflop

Research Chip的用途很有限,因为它的CPU内核还太简单,Intel的下一步目标是利用普通内核来代替当前设计的浮点单元,让Teraflop Research Chip具有进入商业应用的能力,但高功耗显然将会是

Intel要面临的第一个问题─Intel以两个措施来应对:一是让闲置的内核可以进入休眠状态,由此节省能源开销和发热量;二就是引入先进的半导体工艺,毕竟Teraflop Research Chip原型只是采用

65nm工艺制造,正式商用版本将采用32nm甚至22nm工艺,高功耗和发热问题可以得到较好的解决(图6、图7、图8)。

图8 Teraflop Research Chip平台演示海啸预测计算,

以前的计算平台需要一周才能预测,而现有平台仅需三天

硅光技术领域的三大革命性突破

在万亿级芯片的设计中,大的困难在于设计一套高效的传输系统。作为原型芯片,Teraflop Research Chip可以采用电路传输而不会遭遇瓶颈,但随着核心的复杂度提升,传输的数据也将越来越多,众多核心间的协作也要求数据快速传输,Intel与加州大学圣芭芭拉分校联手开发硅光计划,希望能够将光传输技术带入万亿级芯片领域,在过去的多年中,双方已经获得多个突破性成果,距离实用化已指日可待。

1.连续波激光技术:解决光在芯片内传导问题

在2005年2月份,Intel就发布了一项名为“连续波激光(continuous wavesilicon laser,CW

laser)”的硅-光混合技术,这项技术可利用标准半导体工艺制造出可驱动连续光波的硅芯片组件,实现硅片与激光技术的结合。“连续波激光”主要解决传输问题,我们知道,半导体硅材料无法像玻璃光纤一样可以让光线通过,无论对可见光还是紫外线都是屏蔽的,但对红外光来说,半导体硅材料却完全透明,因此如果采用红外光来作为数据传输的媒介,与硅芯片达成结合就具有一定的理论可行性。

图9 连续波激光技术在硅芯片上成功地建立了光波导路径

除了可让光线无障碍透过外,硅光混合还需要解决光信号的控制、传导以及放大等问题,连续波激光技术在这些方面都有了重大突破。在光纤通信系统中,光信号的放大是通过专门的放大系统进行,以便在传输路线中周期性地恢复信号功率。但硅芯片内部不可能容纳这样的放大器,为此

Intel的研究人员发明了一种方法,利用“拉曼效应(Raman effect)”来实现光信号的放大。这项工作的第一步就是在硅片中蚀刻出“波导(waveguide)”─波导是芯片内光线传递的通道,对红外线光来说,硅材料的波导就好比是透明的玻璃光纤,因此当红外光进入波导时,研究人员就可以在芯片内对红外光进行控制及传导。不过,硅片本身无法产生红外光,Intel的研究人员就利用了一个外部光源将红外激光导入芯片内、产生连续完整的激光束。为了形成拉曼效应,硅芯片表面被覆上一层反射性的薄膜(类似高品质太阳镜的反射膜),当红外激光导入到芯片时,一部分激光会照射到薄膜上形成拉曼散射,并在波导内部形成自然原子振动,进而对光信号产生放大作用─与玻璃光纤相比,硅芯片内的拉曼效应强度要高出一万倍以上,信号放大效果极其显著(图9)。

拉曼效应:光照射到物质上会发生弹性散射和非弹性散射,弹性散射的散射光波长同激发光波长相同、而非弹性散射的散射光波长则与激发光波长存在差异,这种现象被称为“拉曼效应”而非弹性散射的光谱则被称为“拉曼光谱”。

2.混合硅激光技术:令硅“自主发光”

在前面的连续波激光项目中,Intel研究人员必须借助外部光源才能将红外光导入到硅片,但在半导体工艺中,导入外部光源并不具可行性。显然,如果要让光子代替电子在芯片内流动,唯一的途径就是让硅材料能够自主发光。

Intel与美国加州大学圣芭芭拉分校(UCSB)的研究人员联手攻关这个项目。2006年9月,双方宣布研发成功名为“混合硅激光(Hybrid Silicon Laser)”的硅光混合技术,打开了迈向硅光混合计算的大门。混合硅激光技术的关键点是实现磷化铟(Indium Phosphide)与半导体硅的结合、并能够以标准硅工艺进行生产─磷化铟被广泛用于光纤通信系统的激光器中、它可以在电压的作用下产生激光,但基于磷化铟的激光器需要逐一进行组合和校准,无法实现计算机产业所要求的大批量、低成本制造。

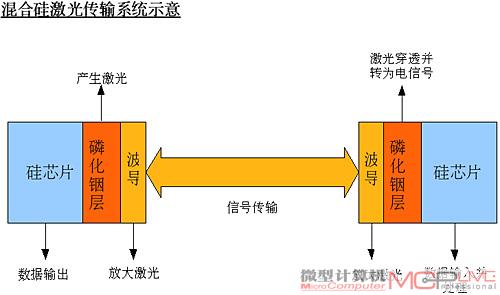

图10 混合硅激光系统示意图

而Intel与芭芭拉分校的研究人员没有将磷化铟作为独立的激光器,而是将它与硅芯片相结合,这样在连续电压信号的驱动下,磷化铟就产生相应的红外激光信号,通过这样的方式,我们就能够将二进制数据加载到红外激光上、这相当于让硅芯片具备直接输出光信号的能力。与之对应,系统内有一套光传输总线,硅光芯片(比如处理器)输出的光信号经过波导放大后、再通过光总线传送给位于目标端的硅光芯片(比如另一枚处理器),同样,光信号会再度进入目标芯片的波导被放大,然后被还原为二进制电信号参与运算,其运算输出结果则会被再度转成光信号、经波导放大后传回(图10)。通过这样的机制,硅芯片间发生的所有数据传输任务都可以借助光技术进行,借此我们能够构建TB/s量级的超高带宽总线。

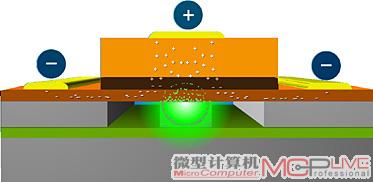

图11 磷化铟薄氧化膜与硅薄氧化膜粘合在一起

混合硅激光芯片的设计方案非常巧妙,其关键点在于如何将磷化铟材料与半导体硅晶圆有机地结合起来─Intel与芭芭拉分校的科学家们在此表现出他们的天才设计:用超低温的氧等离子体(带电荷的氧气)在这两种材料表面都形成一层仅有25个原子厚度的薄氧化膜,然后将两者面对面叠放、同时加热加压,这样磷化铟材料的薄氧化膜与硅晶圆的薄氧化膜就像玻璃粘合剂一样熔合、从而将两种材料熔合为一个整体;之后的工序按照传统的半导体制造工艺进行:设计好波导和电压控制器的集成电路图被印刷到硅晶圆上,这样我们就可以制造出硅光混合型芯片(图11)。

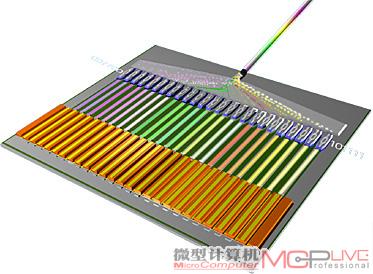

图12 拥有25个混合硅激光器的硅片光传输系统,该系统可实现40Gb/s带宽

作为项目的负责人,芭芭拉分校电气和计算机工程学教授约翰·鲍尔斯(John Bowers)强调该技术的革命性意义:“混合硅激光器能够用于晶圆级、半晶圆级和芯片级的应用,将大规模光学器件与硅平台有机结合起来,终实现硅光子器件的低成本和大批量制造,这将大幅度降低光传输技术的应用门槛”(图12)。

3.硅基雪崩光电探测器:利用半导体工艺生产

连续波激光技术与混合硅激光技术成功地解决了光信号的产生与传输问题,但要让光子在芯片内部代替电子,必须拥有高效率的光电转换手段,否则无法实现光子与电子的对接─毕竟在核心内部,计算信号还是以电子形式存在。也就是说,Intel还需解决光探测的问题。

2008年12月8日,新的喜讯到来:Intel宣布在硅基雪崩光电探测器(Silicon-based Avalanche

Photodetector)研究方面实现了创纪录的进展,新的研究成果使用硅和半导体工艺实现了有史以来高的340GHz“增益-带宽积”。这也意味着硅光芯片的后障碍获得圆满解决,光信号代替电信号将成为真正意义上的现实。

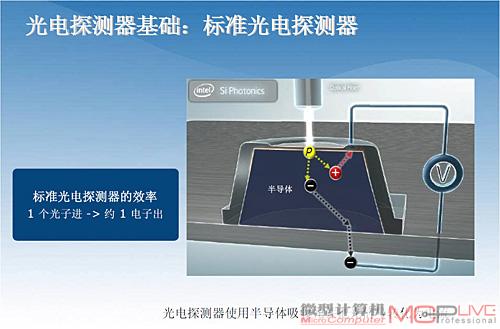

图13 标准光电探测器,转化率约1:1

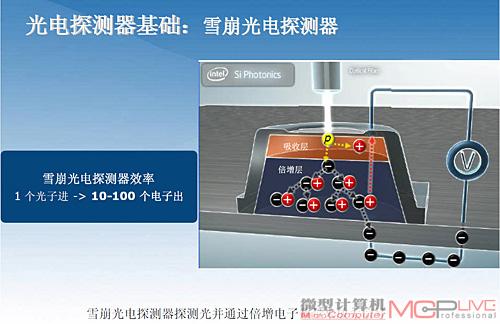

对于硅光电探测技术我们并不陌生,数码相机的CCD/CMOS感光元件、太阳能电池,都是硅光电技术的实际应用,这些产品所用的是传统的光电探测器。这种光电探测器的设计比较简单:一个光子进入探测器,激发半导体部分产生一个电子空穴对。因此只有比较强的光照,才能够输出较强的电流。而“雪崩”光电探测器是在原有的半导体中加入了“吸收层”,在倍增区施加电场,通过吸收层一个光子激发的一个电子来到倍增区,经过系列电离化后产生10~100倍的电子(图13、图14)。

图14 雪崩光电探测器,转化率可高出10~100倍

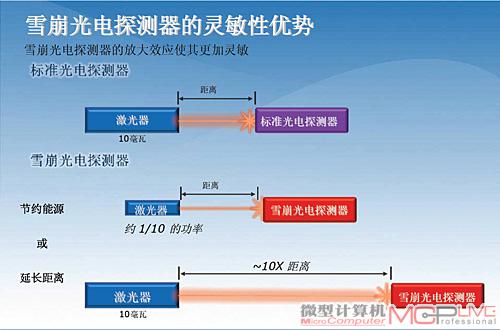

由于转化灵敏度提升十倍以上,那么只要有原先十分之一的光信号,雪崩探测器就可以输出同样的电流─这意味着在其他设施不变的情况下,改用雪崩探测器可以将光纤的传输路径延长十倍以上。或者只要消耗十分之一的能源,就可以得到同样的传输距离。对于万亿级芯片来讲,采用雪崩探测器的好处更多体现在超低能耗(图15)。

图15 两种光电探测器的效果对比

然而,现有的Ⅲ-Ⅴ族雪崩探测器是用于传统光通信领域,这些产品现在已经被广泛采用,但它们无法采用硅半导体工艺进行生产。此次Intel所研发的硅基雪崩探测器很好地解决了这种问题,即它可以像CMOS图像传感器一样在半导体生产线中大量生产,同时也可以轻松做到超微细化的结构(图16)。

图16 Intel硅基雪崩探测器,可采用标准半导体工艺制造,同时又具有更高的性能

凭借压倒性的性能和制造优势,硅基雪崩探测器成功战胜了传统的光电探测器和Ⅲ-Ⅴ族雪崩探测器,将雪崩光电探测器的优势从现在的10Gbps引入40Gbps链路。不过Intel的终目标还是硅基光电技术实现芯片间和芯片内光信号互连,从而将数据传输带宽轻松提升到数以百GB和TB的级别,从上述技术进展来看,我们认为这一天并不会太遥远。

写在后

Intel“万亿级计算”揭示了一个科幻世界般的美好未来:光子代替电子,成为芯片内部不断流动的新血液,这本身就是一件非常酷的事情,何况光传输所具有的带宽优势和能耗优势都是无可比拟的。光传输几乎不会带来任何发热,能源消耗也很低,这可以将芯片的发热水平直接降低30%的幅度。而万亿级通用计算将让PC能够实现现在我们难以想象的新任务,一个革命性的时代即将在未来五年内登场,对此我们翘首以待。